# **Laboratory 5**

(Due date: 002/003/007/010: March 22<sup>nd</sup>, 004: March 23<sup>rd</sup>, 006/008: March 24<sup>th</sup>, 011: March 26<sup>th</sup>)

### **OBJECTIVES**

- ✓ Describe synchronous circuits in VHDL.

- ✓ Learn Testbench generation for synchronous circuits.

### **VHDL CODING**

✓ Refer to the Tutorial: VHDL for FPGAs for examples and parametric code for register.

## FIRST ACTIVITY (100/100)

#### **DESIGN PROBLEM**

# RANDOM MEMORY ACCESS (RAM) EMULATOR:

- The following circuit is a memory with 8 addresses, each address holding a 4-bit data. The memory positions are implemented by 4-bit registers. The resetn (active low) and clock signals are shared by all the registers. Data is written onto (or read from) one of the registers.

- Memory Write (wr\_rd = 1): The 4-bit input DI is written into one register. The address[2..0] signal selects the register to be written. Here, the 7-segment display must be OFF. Example: if address= "101", then DI is written into register 5.

- Memory Read (wr\_rd = 0): The MUX output appears on the 7-segment display (hex. value). The address[2..0] signal selects the register from which data is read. For example, if address= "010", then data in register 2 appears on the 7-segment display. If data in register 2 is "1010", then the symbol 'A' appears on the 7-segment display.

- Only one 7-segment display should be activated.

# wr rd $\cap$ 1 2 E EN 3 add Decoder: Decoder HEX to 7 segments гd 4 5 6

#### **PROCEDURE**

- Vivado: Complete the following steps:

- ✓ Create a new Vivado Project. Select the corresponding Artix-7 FPGA device (e.g.: the XC7A50T-1CSG324 FPGA device for the Nexys A7-50T).

- ✓ Write the VHDL code for the given circuit. <u>Synthesize</u> your circuit to clear syntax errors.

- Use the Structural Description: Create a separate .vhd file for i) Register with enable, ii) Bus MUX, iii) decoder with enable, iv) HEX-to-7 segments decoder (with enable and active-low outputs), and v) top file.

- ✓ Write the VHDL testbench to simulate your circuit.

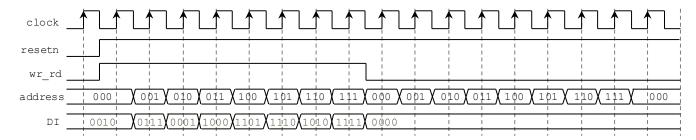

- The testbench should be written according to the timing diagram shown in the figure. There are 8 writes (each on a different memory address), and then 8 reads (each from a different memory address). You must generate a 100 MHz input clock with 50% duty cycle.

- ✓ Perform <u>Functional Simulation</u> and <u>Timing Simulation</u> of your design. **Demonstrate this to your TA**.

- <u>Behavioral Simulation</u>: Add the internal signal DO the waveform view. Go to: SCOPE window: testbench  $\rightarrow$  UUT. Then go to Objects Window  $\rightarrow$  Signal(s)  $\rightarrow$  Add to Wave Window. Then, re-run the simulation.

- If your circuit works as expected, the data written on DI will appear on DO (when wr\_rd=0) for the corresponding address.

- ✓ I/O Assignment: Generate the XDC file associated with your board.

- Suggestion (for Basys 3, use SW15 instead of CPU RESETN for resetn input)

| Board pin names      | CLK100MHZ | CPU_RESETN | SW7   | SW6-SW4                                        | SW3-SW0                          | CA-CG | AN7-AN0 |

|----------------------|-----------|------------|-------|------------------------------------------------|----------------------------------|-------|---------|

| Signal names in code | clock     | resetn     | wr_rd | address <sub>2</sub> -<br>address <sub>0</sub> | DI <sub>3</sub> -DI <sub>0</sub> | CA-CG | AN7-AN0 |

- The board pin names (except CPU\_RESETN) are used by all the listed boards (Nexys A7-50T/A7-100T, Nexys 4/DDR, Basys 3). I/Os: Note that CA-CG and AN7-AN0 are active low; whereas the switches are active high.

- Note: synchronous circuits always require a clock and reset signal.

- ✓ Reset signal: As a convention in this class, we use active-low reset (resetn). As a result, ensure that resetn is tied to the proper board resource:

- Nexys A7-50T/A7-100T, Nexys 4/DDR: For resetn, use CPU RESETN pin. This is an active-low push button.

- Basys 3: There is no active low push button. Thus, for *resetn*, use SW15. Even though SW15 is active high, we can still think of it as active-low *resetn*, where the circuit is reset when the switch position is OFF ('0').

- ✓ Clock signal: Like other signals in the XDC file, you need to uncomment the lines associated with the clock signal and replace the signal label with name used in your code. In addition, there is parameter -period that is set by default to 10.00. This is the period (in ns) that your circuit should support.

- Basis 3: In these lines, replace the label clk with the signal name used in your code (clock): set\_property PACKAGE\_PIN W5 [get\_ports clk] set\_property IOSTANDARD LVCMOS33 [get\_ports clk] create clock -add -name sys clk pin -period 10.00 -waveform {0 5} [get ports clk]

- Generate and download the bitstream on the FPGA and test. Demonstrate this to your TA.

- Submit (<u>as a .zip file</u>) all the generated files: VHDL code files, VHDL testbench, and XDC file to Moodle (an assignment will be created). DO NOT submit the whole Vivado Project.

| TA signature: | Date: |

|---------------|-------|